# Desarrollo del *front-end* de un transceptor RFID pasivo bajo proceso CMOS de 500 nm<sup>1</sup>

Agustín Grosso<sup>1</sup>, Flavio Galimberti<sup>1</sup>, Juan Antonio Tántera<sup>1</sup>, Yao Ming Kuo<sup>1,2</sup>, Jorge Rodríguez Mallo<sup>1</sup>

<sup>1</sup>Universidad Tecnológica Nacional, Facultad Regional Buenos Aires, Departamento de Ingeniería Electrónica, Av. Medrano 951, (C1179AAQ) Ciudad Autónoma de Buenos Aires, Argentina <sup>2</sup>Instituto Nacional de Tecnología Industrial, Av. Gral. Paz 5445, General San Martín, Buenos Aires, Argentina

agrosso@frba.utn.edu.ar

Recibido el 13 de marzo de 2017, aprobado el 15 de junio de 2017

## Resumen

En la presente publicación se describe el diseño del demodulador, generador de *clock*, divisor de *clock*, el rediseño de los módulos de rectificación y regulación, y las pruebas en laboratorio de éstos y del modulador de carga, que forman parte de un circuito integrado (CI) transceptor RFID (13,56 MHz). La manufactura en el proyecto fue realizada a través de MOSIS® (THE MOSIS SERVICE, 2016) en un proceso de fabricación ESTÁNDAR CMOS de 500 nm, usando tecnología cuyo largo mínimo de canal es de 600 nm.

**PALABRAS CLAVE:** CIRCUITOS INTEGRADOS ANALÓGICOS – RFID – MODULADOR – DE-MODULADOR – RECTIFICADOR - LIMITADOR - REGULADOR - CLOCK - CMOS

## **Abstract**

This paper describes the design of a demodulator, a clock generator, a clock divider, the redesign of the modules of voltage rectification and regulation, and the laboratory tests of these and the load modulation, which form part of an integrated circuit (IC) RFID transceiver (13.56 MHz). In this project, the manufacture was realized by means of MOSIS® (THE MOSIS SERVICE, 2016) in a manufacturing process STANDAR CMOS of 500 nm, using technology whose minimum channel width is 600 nm.

**KEYWORDS:** ANALOG INTEGRATED CIRCUITS – RFID – MODULATOR – DEMODULATOR – RECTIFIER - LIMITER - REGULATOR - CLOCK - CMOS

<sup>&</sup>lt;sup>1</sup> Esta publicación forma parte del Proyecto de Investigación y Desarrollo (PID EIUTNBA0003873), denominado "Investigación y desarrollo de un circuito integrado transceptor por radiofrecuencia, pasivo y de bajo consumo" dirigido por Sebastián Verrastro (UTN.BA).

## Introducción

En la presente publicación² se describen las modificaciones de los módulos de rectificación y regulación de tensión, el diseño del demodulador y las pruebas de laboratorio del chip transceptor RFID fabricado bajo el proceso con el que cuenta la Facultad Regional Buenos ai Aires de la Universidad Tecnológica Nacional (UTN-BA).

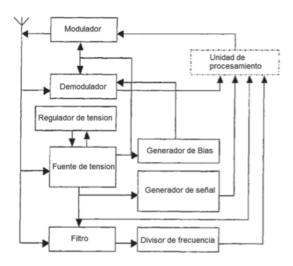

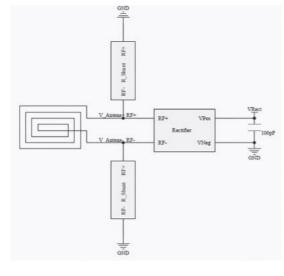

En la Figura 1 se muestran los bloques principales de un *tag* RFID (Lu, 2001).

#### Diseño del demodulador

La comunicación desde el PCD (Proximity Card Device) al PICC (Proximity Integrated Contactless Chip Card) se llevó a cabo mediante una modulación ASK (Amplitude Shift Keying) al 100% con una codificación Miller Modificado (Norma ISO14443 Tipo A). La modulación ASK tiene como característica la variación de la señal portadoras entre dos valores definidos. En una modulación ASK al 100%, la señal, variará entre un nivel de tensión mayor a cero y 0 V (cero Volt).

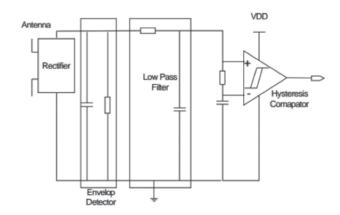

La demodulación de la señal recibida en el PICC, se llevó a cabo a través de varias etapas (Figura 2). En primer lugar, se realizó la rectificación de la señal y la detección de envolvente. En una segunda etapa, se filtró la señal obtenida en la etapa anterior para evitar errores en la próxima fase de tratamiento de señal debido a variaciones de alta frecuencia sobre la señal envolvente. En la última parte, se ingresó la señal ya filtrada a un Schmitt *trigger* (Munish Kumar, 2012) para obtener, a la salida, la señal que representa los datos enviados por el PCD.

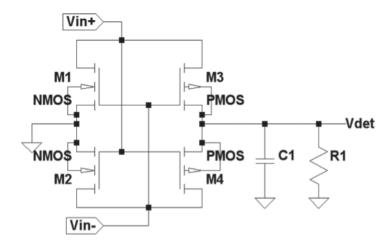

## Rectificador y detector de envolvente

En esta etapa se usó una topología típica de un demodulador de AM (amplitud modulada), la cual se ve en la Figura 3 y se caracteriza por ser un circuito simple, compuesto por un rectificador y un detector (Resistor y Capacitor en paralelo).

A continuación, se realizó el análisis matemático de la topología para obtener los valores de componentes que optimizan el funcionamiento del circuito. Para un análisis más sencillo, se optó por tomar como rectificador a un diodo.

Teniendo en cuenta que el detector de envolvente se compone de un resistor y un capacitor,

Fig. 2. Estructura básica de un demodulador (Zheng Zhu, 2004)

<sup>&</sup>lt;sup>2</sup> Para la elaboración de este trabajo se partió del desarrollo publicado con anterioridad (Grosso, Galimberti, Kuo, 2016), se prosiguió con el diseño y rediseño de algunas etapas y a su medición en el laboratorio.

Fig. 3. Rectificador y detector de envolvente

éste presenta una constante de tiempo  $\tau = R*C$ .

Considerando también que se tiene una señal portadora con una frecuencia igual a  $f_c$  = 13,56 MHz, el capacitor se descarga, entre cada pico de portadora, siguiendo la siguiente ecuación:

$$V'_{pico} = V_{pico}.e^{-\frac{t}{\tau}}$$

Donde T = 1/fc. Si tomamos T  $<< \tau$ , entonces:

$$\nabla V \simeq V_{pico}.\frac{T}{\tau} = \frac{V_{pico}}{f_c.\tau}$$

Entonces, el  $\tau$  de la topología elegida, determinará la ondulación a la frecuencia de la señal portadora que tendrá la señal a la salida del detector de envolvente.

Cuando la señal está modulada en ASK, su tensión pasa, de un valor de tensión definido a un valor mucho menor (cero Volts en nuestro caso). La caída de tensión en el detector

$$V_{caida} = V_{pico} \cdot e^{-\frac{t}{\tau}}$$

e ecuación:

Desde la ecuación anterior, puede analizarse el comportamiento del circuito detector ante el cambio de tensión mencionado. Dependiendo del  $\tau$  del RC, éste será más o menos sensible al cambio de tensión.

Buscando, en la práctica, una buena relación en la respuesta del circuito detector ante el cambio de tensión a la frecuencia modulante y ante el *ripple* a la frecuencia portadora, se toma un  $\tau$  dentro del intervalo de la ecuación siguiente:

$$\frac{1}{f_c} \ll \tau \ll \frac{1}{f_m}$$

Entonces, teniendo 13,56 MHz como  $f_c$  (frecuencia de portadora) y 106 kHz como  $f_m$  (frecuencia modulante) se escogieron los siguientes valores de componente:

$$R = 5 K\Omega$$

;  $C = 30 pF$

Quedándonos la siguiente relación entre frecuencias y  $\tau$ :

$$\frac{1}{13,56 \, MHz} \ll 1,5.10^{-7} s \ll \frac{1}{106 \, KHz}$$

Fig. 4. Señal de entrada y señal de salida del detector de envolvente  $\tau = 0.15 \mu S$

Fig. 5. Filtrado del ripple de 13,56 MHz con filtro RC

## Filtro pasa bajos

Una vez que, la señal modulada que llega al PICC, pasa por el detector de envolvente, ésta, queda con un *ripple* a la frecuencia de la portadora. Para evitar que en la siguiente etapa se produzcan fallas debido a variaciones de tensión no deseadas, la señal de salida del detector, pasa por un filtro (pasa bajos simple) RC cuyo fin, es mitigar las ondulaciones de 13,56 MHz. La frecuencia de corte del filtro deberá estar por debajo de la frecuencia de portadora, para así filtrarla y por encima de la frecuencia modulante, para no afectar la envolvente. Entonces:

$$\frac{1}{106 \text{ KHz}} \ll f_c \ll \frac{1}{13,56 \text{ MHz}}$$

$$fc = \frac{1}{2\pi RC} \approx 3,2 \text{ MHz}$$

$$R = 10 \text{ K}\Omega; C = 6 \text{ pF}$$

# Schmitt trigger

Dado que la señal de salida del demodulador ingresará luego a un sistema digital, ésta debe estar libre de ruido y distorsiones para evitar errores en la información y, por lo tanto, en el sistema encargado del manejo de la información. Una forma de digitalizar una señal, eliminando las perturbaciones que trae, es a través de un Schmitt *trigger*.

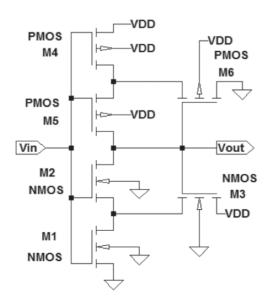

Este tipo de disparador se caracteriza por su naturaleza biestable y por el uso de una histéresis que gobierna los cambios de estados. La topología escogida es la de un inversor CMOS de doble transistor con la adición de un par de transistores que son los que definen los puntos de cambio de estado en la histéresis.

Esta topología, cuenta con la ventaja de poder escoger los puntos de disparo del sistema eligiendo la relación de aspecto de los transistores

Fig. 6. Schmitt trigger CMOS

que la conforman. Las relaciones entre el ancho y el largo del canal de los transistores, tienen efecto en la histéresis del disparador.

Cuando en la entrada del circuito (Figura 6) hay 0 V, los transistores M4 y M5, estarán conduciendo, mientras que el M1 v el M2, estarán en corte. Con esa condición, la salida estará en alto (Vout = VDD). Cuando la tensión de entrada comience a subir y alcance la tensión de umbral del transistor M1, éste comenzará a conducir, pero el M2 se mantendrá apagado. El M1 tenderá a hacer bajar el nodo entre éste y el M2 a GND, mientras que, el M3, que tiene VDD en su gate, hará tender el nodo hacia VDD. Cuando la señal de entrada supere la tensión umbral del M2, entonces, éste comenzará a conducir y la salida tendrá 0 V de tensión, denominando la tensión de entrada que dispara la salida al nivel bajo como VIH (tensión límite que se admite como uno lógico).

Algo similar ocurre con la rama superior del inversor cuando la tensión de entrada comienza a disminuir. Los transistores M4 y M6 harán tender el nodo hacía VDD y GND respectivamente, hasta que el M5 comience a conducir y la salida pase al estado alto, denominando, entonces, la tensión de entrada que dispara la salida al nivel alto como VIL (tensión límite que se admite como cero lógico).

Partiendo del análisis en condiciones de saturación de los transistores M1 y M3 se llegó a la expresión de la VIH en función de las relaciones de aspecto de dichos transistores:

$$I_{DM3} = \frac{\beta_3}{2(V_{GS} - V_{TH3})^2}$$

Siendo

$$\beta = \mu_n * Cox * \left(\frac{w}{L}\right)^2$$

$(\mu_n$ : movilidad de los electrones en el silicio, Cox: Capacidad del Óxido, W: Ancho de la compuerta del transistor, L: Largo de la compuerta del transistor)

Desarrollando y teniendo en cuenta que:

$$V_{TH2} = V_{TH3}; I_{DM3} = I_{DM1}$$

Puede llegarse a la siguiente ecuación:

$$V_{IH} = \frac{V_{DD} + V_{TH1} \sqrt{\frac{\beta_1}{\beta_3}}}{1 + \sqrt{\frac{\beta_1}{\beta_3}}}$$

Haciendo un análisis similar, pero en condiciones de saturación para los transistores M6 y M4, se llega a la expresión de VIL:

$$I_{DM6} = \frac{\beta_6}{2(V_{SG} - |V_{TH6}|)^2}$$

Desarrollando y teniendo en cuenta que:

$$V_{TH5} = V_{TH6}; I_{DM4} = I_{DM6}$$

Puede llegarse a la siguiente ecuación:

$$V_{IL} = \frac{\sqrt{\left(\frac{\beta_4}{\beta_6}\right)(V_{DD} - |V_{TH4}|)}}{1 + \sqrt{\frac{\beta_4}{\beta_6}}}$$

Una vez encontradas las expresiones de VIL y VIH, se buscó una relación entre los tamaños de los transistores, para lograr un óptimo funcionamiento del circuito, evitando errores por ruido de alta frecuencia y distorsiones en la señal de entrada.

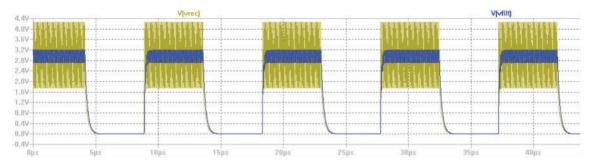

Fig. 7. Tensión de entrada y de la salida del Schmitt trigger

Fig. 8. Tensión de entrada y de la salida del demodulador completo

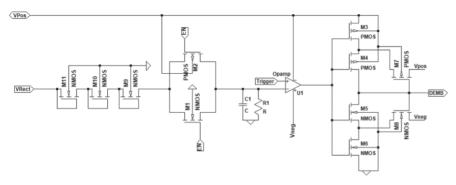

Fig. 9. Esquemático de Demodulador versión B

#### Diseño de Demodulador B

Esta topología, además de estar conformada por el Schmitt *trigger* y un filtro pasabajos, posee en el diseño, un comparador y una entrada de habilitación. Ésta tiene la ventaja de poder ajustar el nivel del comparador externamente. La desventaja es que el amplificador operacional diseñado tiene un tiempo de respuesta (*Slew Rate*) mucho mayor que el Schmitt *trigger*.

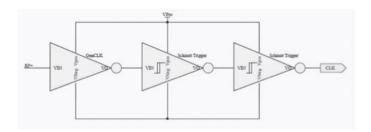

#### Diseño del generador de clock

La finalidad de este circuito es extraer la portadora de 13,56 MHz del lector (PCD).

El *clock* se utiliza principalmente en la parte digital, para sincronizar la comunicación entre PCD y PICC.

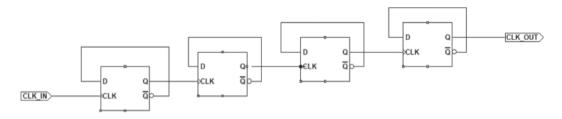

# Diseño del divisor de clock por 16

En esta etapa se usó una topología típica de divisor de *clock*, basada en la realimentación de un Flip Flop D. Cada Flip Flop divide por 2 la frecuencia de entrada.

$$CLK_{OUT} = \frac{CLK_{IN}}{2^{Cantidad\ de\ Flip\ Flops}}$$

El propósito de usar divisiones de frecuencia para la parte digital es bajar el consumo del chip. Esto es muy importante ya que toda la energía es entregada por el PCD.

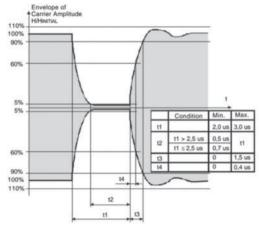

El PCD manda información al PICC (Figura 12) usando modulación ASK al 100% (según la norma ISO 14443-A). Esto significa que hay instantes de tiempo (3 microsegundos aproxi-

Fig. 10. Esquemático del generador de clock

Fig. 11. Esquemático del divisor de clock por 16

Fig. 12. Modulación ASK 100% PCD -> PICC (ISO 14443-A)

madamente) en que el PCD deja de entregar energía al PICC y se tiene que almacenar la energía para el correcto funcionamiento del sistema. Por eso es muy importante el consumo de la parte digital. Se trata de trabajar a la menor frecuencia posible y de esta forma, bajar la potencia dinámica.

#### Rediseño del Limitador

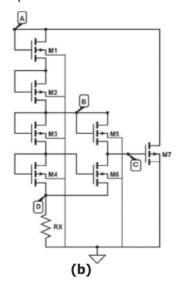

Con el objetivo de mejorar los comportamien-

(a)

tos observados en las mediciones (detallados en la sección Mediciones de Laboratorio (IV)), se optó por modificar la topología empleada en el diseño de la publicación anterior Figura 13 (b) (Grosso, Galimberti, Kuo, 2016)

En la Figura 13 (a) se observa la topología implementada. El funcionamiento de esta topología es similar al de la Figura 13 (b), la diferencia es que el transistor M6 se activa cuando:

Fig. 13. (a)Limitador (NAPONG PANITANTU), (b)Limitador (Grosso, Galimberti, Kuo, 2016)

Siendo:

lo que ocurre cuando el transistor M5 se encuentra en saturación. Dicha situación se logra cuando la tensión sobre el *gate* del transistor M5 es

$$Vgs6 = Vrf - Vds5$$

$$Vgs5 > (Vrf - Vgs1 + Vgs2 + Vgs3 + Vgs4)$$

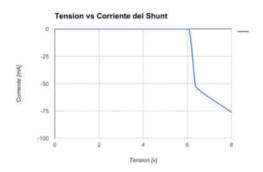

En función de esto se diseñó la topología para que a partir de los 6 V comience a operar el transistor M6. En la figura siguiente se observan resultados obtenidos en la simulación de este módulo.

Fig. 14. Simulación del barrido de DC del limitador

Se puede apreciar que, entre los 0-6 V pico de tensión aplicada a los terminales de la antena, no presenta consumo de corriente y partir de los 6 V en adelante el limitador comienza a operar.

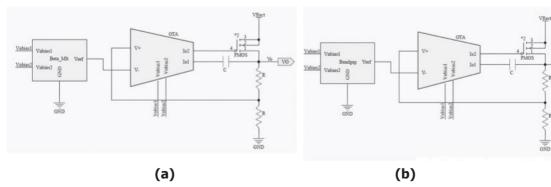

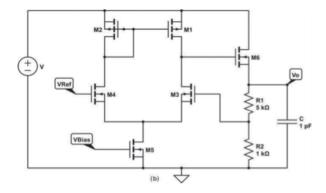

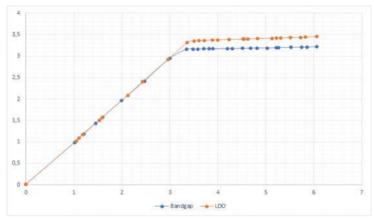

#### Rediseño del regulador

Se realizó el diseño de dos reguladores, uno empleando como fuente de referencia un *Bandgap* (Grosso, Galimberti, Kuo, 2016) y otro diseño con una fuente de referencia Beta multiplier (Baker, Capítulo 20) para la polarización de los circuitos analógicos.

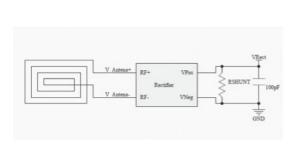

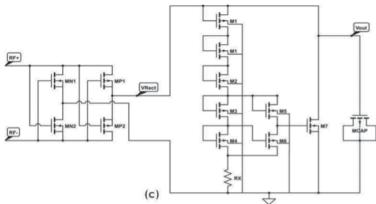

#### Front-end analógico

A diferencia de la publicación anterior (Grosso, Galimberti, Kuo, 2016), en el presente trabajo, se encuentran interconectados todos los módulos (rectificador, LDO, Limitador, Modulador, dos topologías de demodulador y un generador de *clock*) para probar el funcionamiento en conjunto y, además, se incluyeron módulos independientes (regulador y del divisor de *clock*) para pruebas.

En un principio, el primer módulo subsecuente a la antena, era el rectificador y, acoplado a este, se encontraba el limitador (RShunt) junto con los otros módulos como se presenta en la Figura 24 (a).

Al realizarse el *layout* de dicho circuito, se observó que las líneas de metal ruteadas desde los pads de la antena hasta el regulador, debían tener dimensiones importantes en función de la corriente máxima que ha de circular por ellas (en nuestro caso frente al máximo acoplamiento entre las antenas del lector y del chip). Para evitar estas pistas de gran tamaño se realizó la configuración que se presenta en la Figura 24 (b).

En esta configuración se observa la presencia de no uno sino de dos limitadores (uno por cada conector de la antena) previo al rectificador. La finalidad de dicha implementación no es solo asegurar la protección de los transistores MOS del rectificador, sino, también, reducir la complejidad de ruteo de las líneas de metal cuyo ancho es importante hasta la entrada del rectificador.

Fig. 15. Circuitos empleados en los reguladores: (a) Regulador con Beta Multiplier, (b)Regulador con Bandgap

(a) (b)

Fig. 16. (a) Primera distribución del rectificador y limitador (b) Distribución implementada

Posterior al rectificador, las dimensiones de las líneas de metal, se reducen en función del consumo de los circuitos subsecuentes.

#### Mediciones de laboratorio

Se realizaron las mediciones de dos chips. El Primer Chip contiene los módulos descriptos en la anterior publicación (Grosso, Galimberti, Kuo, 2016), mientras que el Segundo Chip posee los módulos diseñados y rediseñados desarrollados en el presente trabajo.

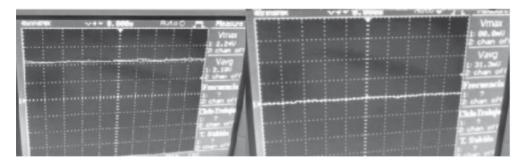

## I. Modulador de carga

#### A. Primer Chip

La topología del modulador de carga integrado, responde a la topología mostrada en la siguiente figura

Fig. 17. Modulador de carga (Grosso, Galimberti, Kuo, 2016)

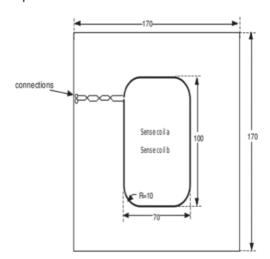

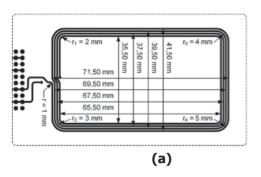

Basándonos en las normas de testeo (ISO/IEC10373) se realizó la fabricación de una antena para las pruebas de laboratorio del chip. La inductancia mostrada por esta antena fue de 1,6 µHy, obteniendo, para una resonancia a 13,56 MHz, una capacidad paralela necesaria de 88 pF.

Fig. 18. Antena para testing (ISO/IEC10373)

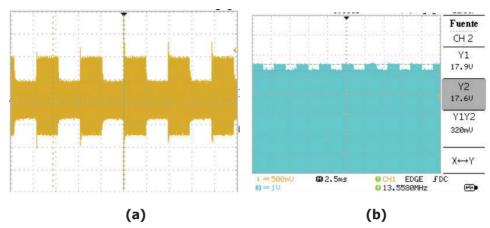

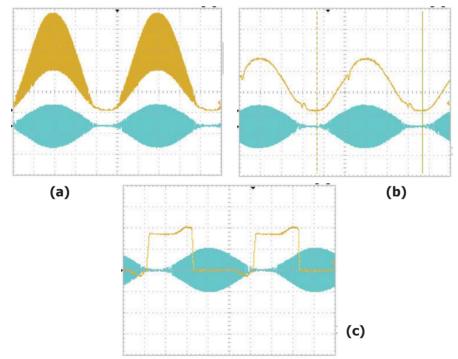

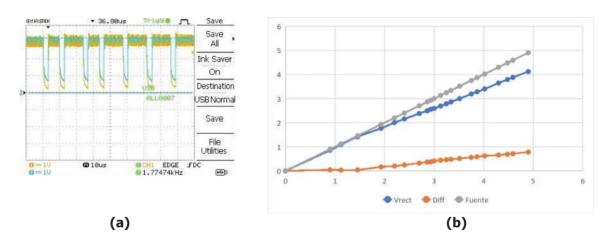

Se probó el módulo mediante un generador de señales, excitando los gates de los transistores que conforman el modulador con un tren de pulsos de 5 V de tensión máxima y una frecuencia de 1 kHz, y se observó una modulación de buena profundidad en la antena de la tarjeta como se observa en la Figura 19 (a). Cuando los *gates* son excitados con la señal en alto (5

Fig. 19. (a) Modulación en la antena de la tarjeta, (b) Modulación en la antena del lector

V), las resistencias de 300 ohmios se colocan en paralelo al tanque resonante y la tensión inducida en éste varía.

La señal observada en el tanque resonante presentó una profundidad de 540 mV, mientras que la tensión pico a pico fue de 2,48 V.

La variación de carga y, por lo tanto, de tensión en la antena de la tarjeta, se refleja en la antena del lector. La variación reflejada descripta mostró una profundidad de modulación de 320 mV sobre la portadora de 13,56 MHz de 37,2 V de tensión pico a pico (Figura 19 (b)).

Estas mediciones fueron hechas sobre el modulador de carga como módulo independiente, sin otros módulos conectados a la antena, por lo que no se tuvo en cuenta posibles capacidades u otras influencias de los demás módulos en las correspondientes pruebas.

#### B. Segundo Chip

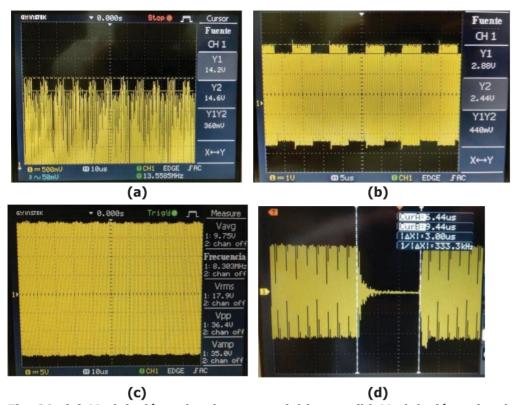

A diferencia de las mediciones del modulador de carga del primer chip (Figuras 19 y 20), en éstas, el modulador se encuentra internamente conectado a los pads de la antena, por lo que se puede extraer información de su comportamiento con respecto a la influencia de los demás módulos acoplados a dichos *pads*.

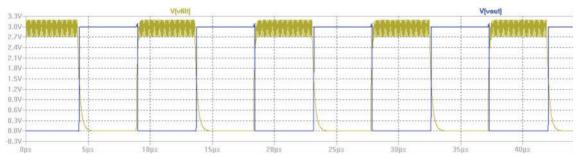

Al momento de realizar la medición se conectó, a la entrada del modulador, una señal cuadrada de 3,3 V de amplitud con una frecuencia de señal de 100 kHz.

En la prueba del correspondiente módulo, la

señal sobre la antena del lector, presentó una profundidad de modulación de 360 mV, con una tensión pico máxima de 14,6 V, como se observa en las Figuras 20 (a) y 20 (c).

Sobre la Figura 20 (b) se aprecia la modulación sobre la antena bajo norma (Figura 31 (b)) conectada al chip. Se puede observar una profundidad de modulación de 440 mV máxima y una tensión pico de 2,88 V.

En la Figura 20 (d) se muestra la modulación al 100% sobre la antena del chip. De esta prueba se concluye que, para la futura parte digital del chip, no habrá *clock*, en ciertos lapsos temporales, durante la recepción de información.

# II. Demodulador

#### A. Discreto

Las mediciones de este módulo fueron hechas sobre un diseño discreto con la misma topología integrada en el chip.

Una de las desventajas de hacer las pruebas sobre una placa discreta es que no se puede trabajar con las relaciones de aspecto de los transistores, lo cual marca los puntos de disparo en la histéresis del Schmitt *trigger*.

Se excitó, directamente, al circuito con una señal modulada en AM al 100% por una senoidal de 1 V de tensión y de, alrededor, de 1 kHz y se midió la respuesta de los distintos módulos que lo componen (detector de envolvente, filtro y Schmitt *trigger*).

Fig. 20. (a) Modulación sobre la antena del lector, (b) Modulación sobre la antena del chip, (c) Tensión pico a pico sobre la antena del chip sin conectar, (d) Modulación ASK 100%

Fig. 21. Capturas del osciloscopio. (a) Señal de excitación (celeste) y señal luego del detector de envolvente (amarilla); (b) Señal de excitación (celeste) y señal luego del filtro RC (amarilla); (c) Señal de excitación (celeste) y señal luego del Schmitt trigger (amarilla)

# B. Segundo Chip

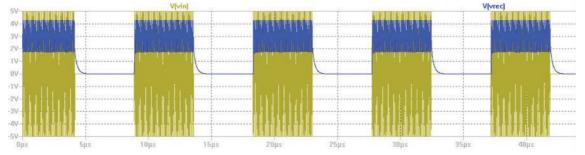

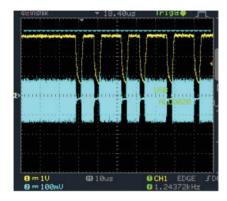

En las mediciones (Figura 22) se observó el funcionamiento de los demoduladores. Este funcionamiento muestra una discrepancia con el comportamiento esperado debido a anomalías en el conexionado entre módulos a causa de alguna posible dispersión del proceso.

Fig. 22. Demodulador A (Amarillo), Demodulador B(Azul)

## III. Regulador de Tensión

## A. Primer Chip

Se observa, en la Figura 24, el funcionamiento de la LDO (Grosso, Galimberti, Kuo, 2016). El análisis de comportamiento, reflejó la necesidad del aumento en las dimensiones del transistor M6 y ajustes en la fuente de referencia *Bandgap*.

## B. Segundo Chip

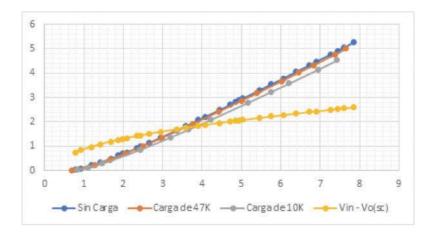

Estas mediciones corresponden al regulador como módulo independiente, sin los efectos de los otros módulos en su funcionamiento.

De las mediciones realizadas con el banco de medición (Figura 31 (a)) se observó que tanto la LDO con fuente de referencia *Bandgap* (Figura 15 (b)), como la LDO con fuente de referencia Beta Multiplier (Figura 15 (a)) presentan una respuesta plana pasados los 3,3 V de tensión de entrada. Esto muestra que los ajustes,

Fig. 23. LDO (Grosso, Galimberti, Kuo, 2016)

Fig. 24. Mediciones realizadas sobre la LDO

Fig. 25. Variación Fuente DC vs Salida de LDO *Bandgap* (azul) y LDO *Beta Multiplier* (naranja)

Fig. 26. Rectificador, Limitador y Capacitor (Grosso, Galimberti, Kuo, 2016)

Fig. 27. (a) Barrido de tensión DC (Figura 19), (b) Barrido de tensión DC. Naranja (Tensión de salida) Azul (Corriente drenada por el limitador)

realizados en base a las pruebas en el primer chip (Figura 24), fueron acertados.

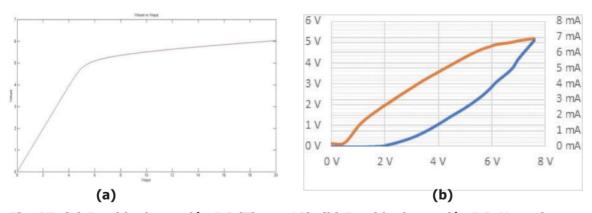

IV. Limitador y Rectificador

A. Primer Chip

La estructura del dispositivo integrado a testear

corresponde al de la Figura 26. Se comparó lo obtenido a través de la simulación (Figura 27 (a) contra las mediciones en el laboratorio (Figura 27 (b)) y se obtuvo que el comportamiento del dispositivo se asemeja a las simulaciones realizadas durante el proceso de diseño, lo que lo vuelve apto para la protección de los módulos subsecuentes frente a tensiones elevadas.

Fig. 28. Captura del Osciloscopio

Fig. 29. (a) Salida del Rectificador y LDO. (b) Variación de DC entrada vs Salida Rectificador

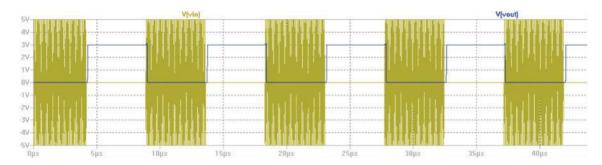

Se midió el mismo dispositivo conectando la antena, acoplándose al lector.

Cuando se conectó la antena y acopló con el lector se observó, en primera instancia, como máximo una tensión de 2,24 V, para posteriormente decrecer abruptamente a 80 mV (Figura 28). Este comportamiento se debe al encendido temprano del drenado de corriente a través del shunt.

## A. Segundo Chip

En la Figura 29 se observa que a medida que se incrementa la tensión de entrada, la caída que ocurre en el rectificador aumenta. Esto verifica que el rectificador presenta una caída de tensión apreciable, la cual conlleva a que el LDO opere con un nivel de tensión menor del que podría obtenerse.

Se obtuvo que, en el rectificador, se produce una caída de tensión sobre lo que limita el shunt dejando, a la entrada del regulador, alrededor de 3 V pico. Podemos observar que la

alimentación del chip decrece linealmente con la modulación del lector.

V. Generador de Clock y Divisor de Clock

## A. Segundo Chip

Las mediciones sobre el generador y divisor de *clock* se vieron afectadas por las características capacitivas que presentan los *pads* del chip. Surge, entonces, la necesidad de fortalecer la etapa de buffer entre la salida de esta etapa y el pad de salida.

#### VI. Banco de medición

Para el momento de realizar las mediciones del chip se construyó una placa de prueba, en la cual poder colocar el encapsulado para posterior medición como se observa en la Figura 31.

La antena que se fabricó para el testeo del chip

Fig. 31. (a) Antena para testing (ISO/IEC10373), (b) Kit de medición del chip

se realizó en base a la norma (ISO/IEC10373/ Anexo D). En la figura siguiente se puede observar el diseño empleado.

Los módulos fueron testeados mediante un kit NFC de Arduino, un generador de señales, y una fuente de laboratorio.

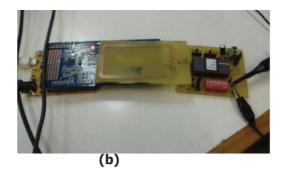

VII. Layout

A continuación, se muestra el *layout* completo del segundo chip diseñado:

Fig. 32. (a) Full *Layout* Chip, (b) Fotografía del Chip Zoom 1x, (c) Fotografía del Chip Zoom 10x, (d) Fotografía del Chip Zoom 50x

## **Conclusiones**

Por lo observado en las mediciones presentadas en este trabajo, se decide la optimización de la etapa de rectificación para la mejora en la operación del regulador, buscando, con esta mejora, minimizar el consumo para cuando el chip se encuentra sin alimentación por la modulación en amplitud del 100%. Otra mejora que se plantea a futuro será el agregado de buffers a la salida y entrada de las etapas digitales, para poder estudiar las salidas del generador, divisor de *clock* y demás etapas con señales de alta frecuencia.

# **Agradecimientos**

El grupo de investigación le agradece a Mentor Graphics® y Synopsys Inc.® por permitirnos el acceso al software a través de sus respectivos acuerdos académicos. También hemos de agradecer a Mosis® por permitirnos realizar la manufactura de los circuitos integrados presentados en este trabajo. Al departamento de Ingeniería Electrónica de la UTN.BA por proveernos del instrumental para las mediciones realizadas, y a los ingenieros Sebastián Pazos, Fernando Aguirre, Francisco Badenas y Andrés Fontana del Laboratorio de Micro y Nano Electrónica por sus consejos y su ayuda en la utilización de la herramienta.

#### Referencias

GROSSO, A.; GALIMBERTI, F.; KUO, Y. M.; AGUIRRE, F.; PAZOS, S.; RODRIGUEZ MALLO, J. y VERRASTRO, S., (2016), "Desarrollo de un circuito integrado transmisor RFID pasivo", en Universidad Tecnológica Nacional, Facultad Regional Buenos Aires, Av. Medrano 951, (C1179A-AQ), Ciudad Autónoma de Buenos Aires, Argentina.

ISO/IEC JTC1/SC17 (2010-04-12), Cards and personal identification.

LU, CHAO; LI YONG-MING, (2001), "The RF Interface Circuits Design of Contactless IC Cards", en Institute of Microelectronics, Tsinghua University, Beijing, China, 100084.

GRAY; HURST; LEWIS; MEYER; "Analysis and Design of Analog Integrated Circuits", Quinta Edición.

MENTOR GRAPHICS, (2016) www.mentor.com, Oregon, USA.

MUNISH KUMAR, PARMINDER KAUR, SHEENU THAPAR, (2012), "Design of CMOS Schmitt Trigger", International Journal of Engineering and Innovative Technology (IJEIT), Volume 2, Issue 1, July 2012.

NAPONG, PANITANTU; APERADEE, YORDTHE IN; WATCHARAKON, NOOTHONG; APISAK, WORAPISHET; AND MANOP, THAMSIRIANUNT; "A CMOS RFID transponder", Thailand IC Design Incubator (TIDI), National Electronics and Computer Technology Center, Thailand. R. JACOB BAKER, "CMOS Circuit Design, Layout, and Simulation", Third Edition. SYNOPSYS INC., (2016) Synopsys Design Compiler, www.synopsys.com California, USA. ZHENG ZHU, (2004); "RFID Analog Front End Design Tutorial", en Auto-ID Labs.